J1850 Core

The core supports both PWM and VPW modes of operation, allowing data rates of 41.6 and 83.3 Kb/s for PWM and 10.4 and 41.6 Kb/s for VPW. An external transceiver chip is required to drive a J1850 bus at the proper voltages, as they are beyond the output capabilities of FPGAs.

J1850 Core Overview

J1850 uses CSMA/CR arbitration, which allows non-colliding transmission without a bus master. The core will listen for the specified listening period before beginning transmission, after which a collision resolution scheme based on message prioritization is used to resolve multiple simultaneous transmissions. The J1850 core will cease transmission if it has a lower priority than another J1850 node on the bus.

The core includes both transmit and receive paths, and the ability to automatically dispatch an In-Frame Response (IFR) data field, when an IFR is requested by received frame. This is done without requiring servicing by the processor.

FIFOs are provided for both the transmit and receive paths, to allow the processor to queue multiple transmissions to the J1850 bus, and allow for delay if the core must wait for bus priority. This functionality is provided through use of a command code which allows the interpretation of the written byte as header information, address, or data bytes. If the core looses an arbitration, it waits until the quiet period is satisfied and retries the transmission automatically. Similarly multiple received frames can be queued before readback by the processor.

FIFO status can be monitored by the processor, or a programmable interrupt can be configured upon frame receipt.

P(X) = X8 + X4 + X3 + X2 + 1

The data frame is shifted through the CRC circuit on the transmission side, producing a CRC byte which is appended to the end of the frame. The receiver shifts the incoming frame, including the CRC byte, through the CRC circuit and this CRC checker will always output 0xC4 if the CRC passes, regardless of frame content.

To assist in generation of the synchronous j1850 clock tick frequency a fractional clock generation RTL circuit can be provided to produce:

where

Fout ≤ 1/2 x Fin

Feature Summary

- SAE J1850 compatible

- Suitable for on- and off-road vehicle internal communications

- Fully synchronous (single system clock)

- Supports PWM and VPW modes of operation

- Automatic IFR generation

- Automatic message retry

- TX and RX buffering

- Generic feature control, synthesize only the features needed (for area savings)

- Behavioral model available for verification

- Test benches available for verification and example of operation

Resource Utilization

The J1850 core is not limited to any vendor specific implementation. Versions are available for all major FPGA vendors, and can be created for any custom ASIC application. The following tables show typical resource requirements.

AMD Utilization Report

| Family | FFs | LUTs | BRAMs (18K) |

|---|---|---|---|

| Virtex 7 | 950 | 1092 | 2 |

| UltraScale | 948 | 1090 | 2 |

Altera Utilization Report

| Family | ALMs | FFs | LUTs | BRAMs (20K) |

|---|---|---|---|---|

| Agilex 5 | 1029 | 1629 | 1276 | 2 |

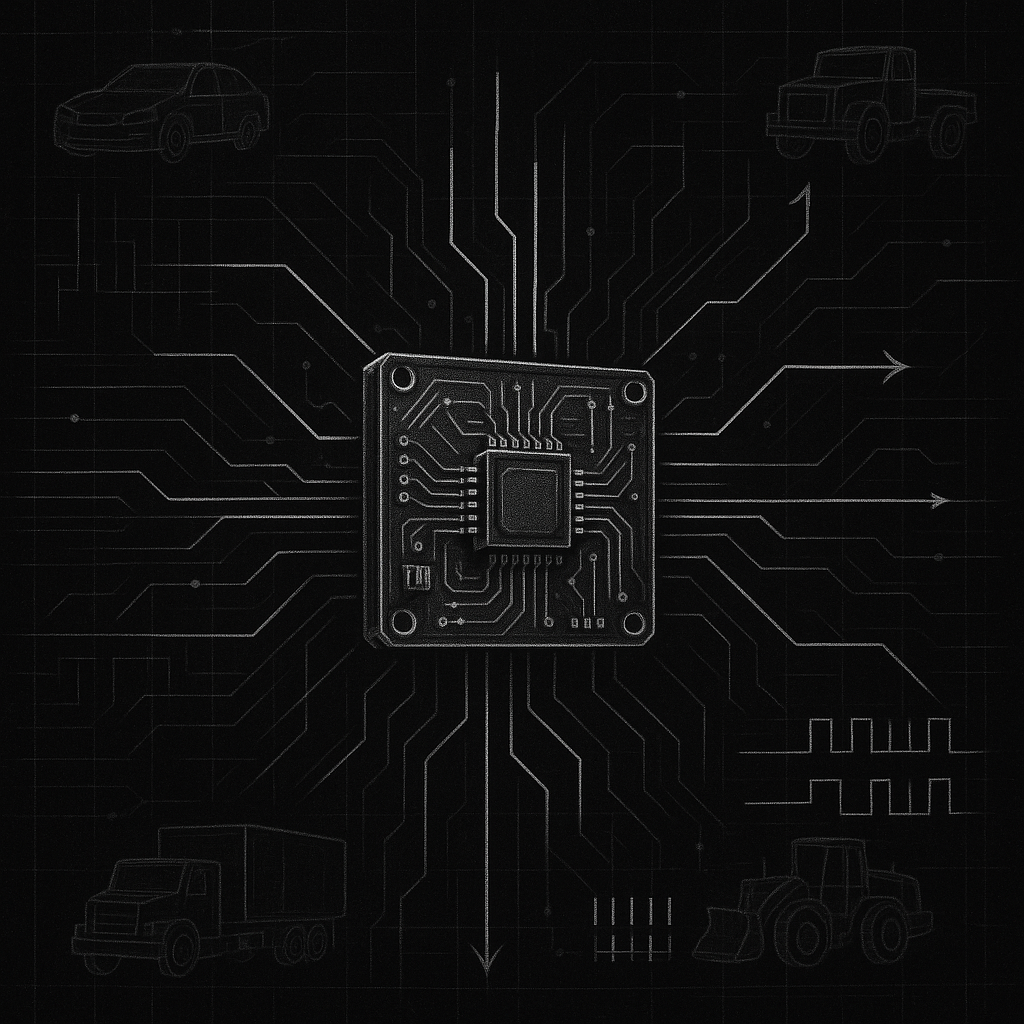

Block Diagram

Optional wrappers are available to connect to standard PLB, AXI, and Avalon local interfaces.

Figure 1 – J1850 Interface Block Diagram